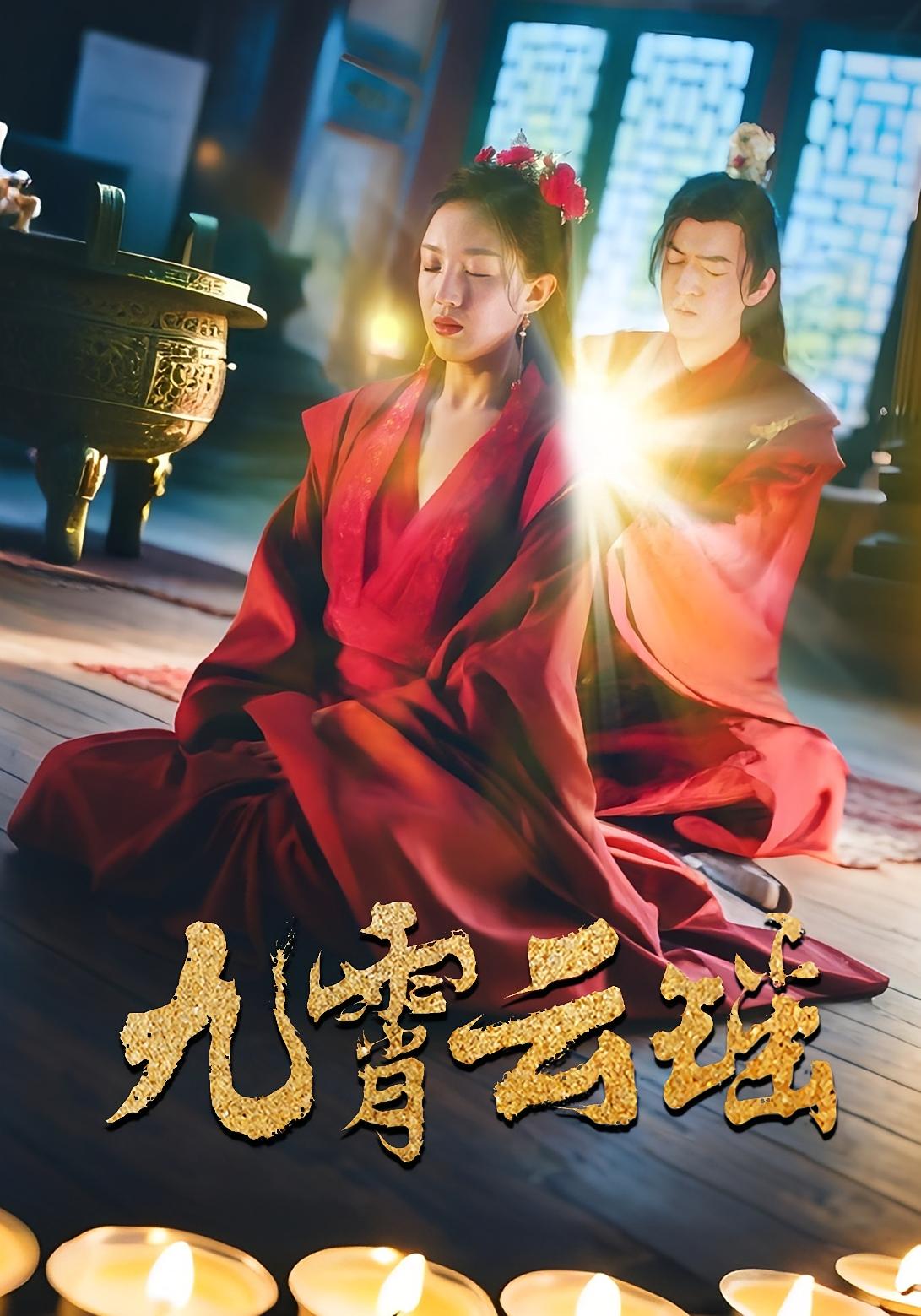

【短剧】赤帛惊九重 女性成长·逆袭·全79集 姜熙饶&张层层&张振宇

短剧介绍

林音身为骠骑将军林峰之女,因父亲林峰救驾身死而被皇上体恤,却没有生活在皇帝赐下的豪宅中,而是另起炉灶,在集市中居住,每天靠制衣、刺绣维持生计。王尚书的女儿王如霜因在选秀中落选而心生怨怼,将制衣的林音母亲何莲衣当成了发泄口。何莲衣被王如霜虐打,林音为给母亲找回公道,先到衙门告状,结果官官相护,她被打了板子扔了出来。不服气的林音,后又去宫门前告状,结果被王如霜带人绑到尚书府。

短剧热评

屎????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????????

好看好看好看好看好看好看好看好看好看好看好看好看好看好看

就喜欢看大女主成长剧,这部剧拍得很好哇,剧情很吸引人,演员演技也好好,是部不错的剧

古装剧一般拍的还行,这个除外

男主演技还要加油女主演技还要加油,剧情还要精品化

客观真实好看的一部剧。

∽的确精彩好看,悬念!

还行吧,剧情有点曲折,对政府拥军优属有点指导意义。

好看非常好看超级好看无敌好看巨好看

没苦找苦硬吃,一直被虐感动谁呢,看着窝火

短剧演员

短剧下载

二维码为夸克网盘链接,扫码免费下载

版权说明

1、本站不保存、不存储任何实质资源,以上二维码指向为网盘资源链接,其内容归对应版权方所有2、如有侵犯版权的情况,请点击下面举报/反馈按钮反馈或发送邮件[email protected]投诉说明情况3、我们核实后将第一时间删除相关内容,谢谢理解和配合