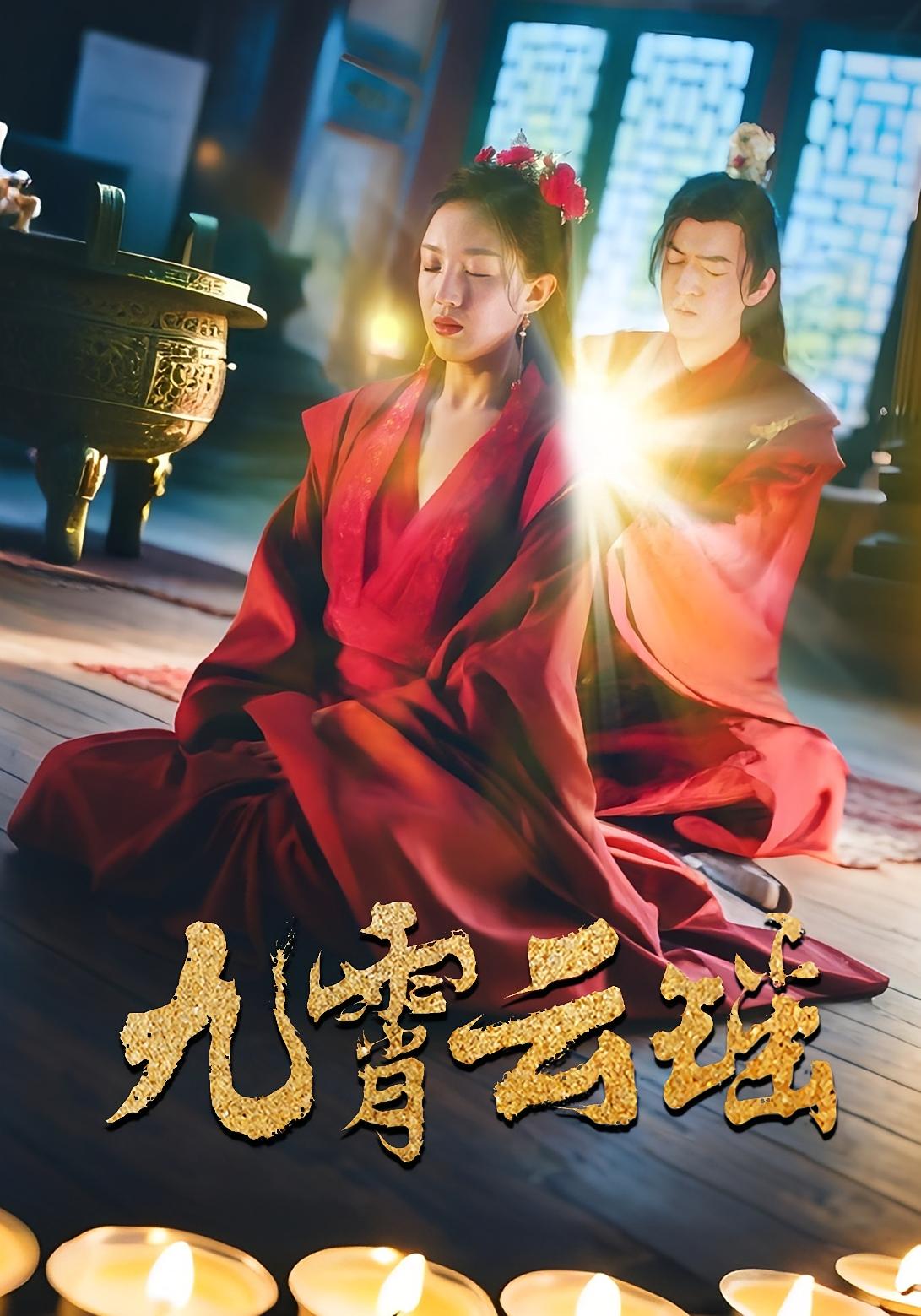

【短剧】嫁给猎户后的悠然生活 奇幻爱情·穿越·全125集 王千硕&曲笑孝&张凤鑫

短剧介绍

李婉晴在与朋友夜市撸串庆祝时,因遇到打架被啤酒瓶砸到脑袋,又被人从背后推搡、踹脚而昏迷。再次醒来,她穿越到了遥远的大舜国。穿越后的李婉晴利用自己的中药学知识治病救人、制作一些独特的药品。在与猎户共同生活的过程中,两人从陌生到熟悉,逐渐产生感情,一起面对生活中的困难。

短剧热评

好看,女主不矫情,男主不愚孝

多来点这种温馨日常的剧吧!!!

超好看,平常的生活,甜蜜的夫妻,好好看[送花][送花][送花]

呆头鹅好可爱[爱慕][爱慕]男主就是宠老婆吃肉肉[爱慕][爱慕][爱慕]

推荐一下这个剧超及好看????

太好看了,羡慕男女主的生活[送花][送花][送花][送花][送花][送花][送花]

好看[爱心][爱心][爱心][偷笑][偷笑][偷笑]

这个剧真的很甜,男女主演的很到位!

我喜欢这种,看着一点也不糟心,小夫妻的日子看着甜甜的

曲笑孝[送花]王千硕[送花]

冲着女主曲笑孝看的这部剧,很喜欢女主笑起来的样子,整部剧怎么说呢,没有虐心,没有搞笑,就很日常的生活,开局就结婚,没误会,整部剧看起来很轻松,我也很轻松的一集一集的看到了最后一集

虽说温馨平淡,也算是个甜剧,但是这些亲戚就如蚊蝇般在耳旁嗡嗡嗡,并非是脱离家里,只是太过繁杂了

笑孝的剧从不让人失望,本以为又是那些套装剧情,没料到竟是这么贴地气,细水流长的种田剧情,虽然有空间金手指,但没有啥隐藏身份,夫妻两人知道自己要什么,低调有原则的生活,完全不憋屈,一直相亲相爱,真的很好看,希望可以一直看下去的剧,太赞????????了

且不说演员演技怎么样,就单单凭借这实实在在的日常生活,就觉得幸福溢满屏。真的很贴近现实生活的一部剧,除了空间以外,其它都比较真实,所以看起来就觉得只要夫妻两个努力,就一定会过好。没什么为这个小家庭而努力更让人踏实的啦。超级喜欢这样的短剧。[赞][赞]

温馨平淡家长里短,舒服的种田文。

平凡夫妻,平常日子。上山打猎下山卖药。置办田庄房产铺子,生儿育女,发家致富。柴米油盐,家常里短。父母兄弟,媳妇妯娌。老百姓的生活全都有,不错!

精准狙击种田文爱好者,剧情什么的都挺还原此类小说,喜欢种田文的不要错过。

剧情还算可以,男女主演技不错,是个生活甜剧,没有争权夺利,没有误会,男女主靠着空间过着平平淡淡的生活。男主对女主算是一见钟情,对女主很宠,女主的话,一起发家致富。男女主吻戏多,几乎每集都有吃肉肉,放心追

又接地气又甜蜜????太好看了[爱慕][爱慕][爱慕]强烈推荐大家

这剧好温馨好喜欢这种田园生活,平平淡淡过好每一天,日出而作,日落而息。这剧虽然有125剧,竟然觉得不够看,太羡慕男女这种生活了,男女主演技很好很自然就感觉这不是在拍戏就像他们本身就是这样生活的[爽][爽][爽]

温馨平淡,不知不觉就看完了,本来看有一百多集还怕长呢,但是没想到看完了还想看呢

家长里短,平淡温馨,很舒服的一部剧,不知不觉就看完了。男女主演技挺好的,不突兀,不出戏。四搭了果然很熟悉,很自然。

这一句剧情平淡了一些,嗯援助的父母是有些偏颇,但是不像其他剧那么严重,动不动就撵出去,动不动就打他一顿,还有女主的家庭,也没说是啥样的也没有女主的其他亲戚来找麻烦,整个剧情来说比较平淡。但演技还是可以的,他们眼都比较不错

超级甜,男女主时不时就吃肉 看的嘎嘎爽,剧情是细水流长的 ,看腻了什么打脸嘲讽剧情,看看这样的淡淡小夫妻之间过的小日子真的很解腻

哈哈哈这是这两个人搭的第几部了?都是挺温馨的剧,好喜欢这种类型[爱慕][爱慕][爱慕]

这部剧的风格就是那种娓娓道来的叙事风格~家里四兄弟的人物性格也刻画的很贴近现实~特别是家里老二那个自私自利理直气壮的嘴脸~还有虽然不离谱但有点和稀泥的公婆~不知不觉就看完了~演员也都演得挺自然的~推荐~

剧情挺温馨的 男女主角演技也挺好 不像有些演员挺浮夸的 总而言之这部剧挺不错的值得一看

短剧演员

短剧下载

二维码为夸克网盘链接,扫码免费下载

版权说明

1、本站不保存、不存储任何实质资源,以上二维码指向为网盘资源链接,其内容归对应版权方所有2、如有侵犯版权的情况,请点击下面举报/反馈按钮反馈或发送邮件[email protected]投诉说明情况3、我们核实后将第一时间删除相关内容,谢谢理解和配合